Member-only story

Shared and Distributed Memory in Parallel Computing

In parallel and distributed computing, memory management becomes crucial when dealing with multiple processors working together. Two prominent approaches exist: shared memory and distributed memory. This tutorial will delve into these concepts, highlighting their key differences, advantages, disadvantages, and applications. Visit the detailed tutorial on Parallel and Distributed Computing.

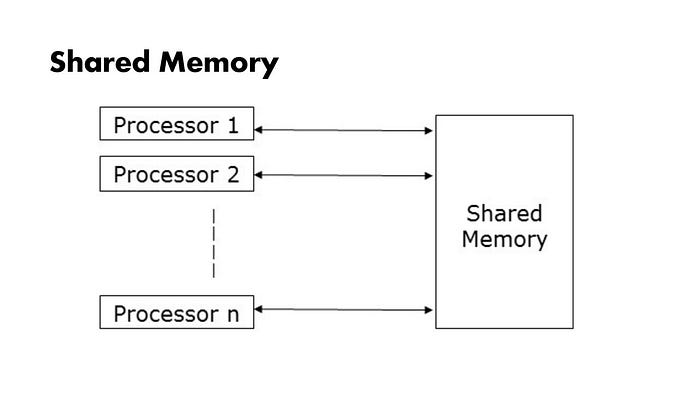

Shared Memory

Shared memory systems provide a single, unified memory space accessible by all processors in a computer. Imagine a whiteboard where multiple people can write and read simultaneously.

Physically, the memory resides in a central location, accessible by all processors through a high-bandwidth connection like a memory bus. Hardware enforces data consistency, ensuring all processors see the same value when accessing a shared memory location.

Hardware Mechanisms for Shared Memory

Memory Bus: The shared memory resides in a central location (DRAM) and is connected to all processors via a high-bandwidth memory bus. This bus acts as a critical communication channel, allowing processors to fetch and store data from the shared memory. However, with multiple processors vying for access, the bus can become a bottleneck, limiting scalability.

Cache Coherence: To ensure all processors see the same value when accessing a shared memory location, cache coherence protocols are implemented. These protocols maintain consistency between the central memory and the private caches of each processor. There are various cache coherence protocols with varying trade-offs between performance and complexity.

Synchronization and Coordination

Shared memory programming offers a simpler model compared to distributed memory, but it’s not without its challenges. Since multiple processors can access and modify shared data concurrently, ensuring data consistency and preventing race conditions is crucial. Programmers need to employ synchronization primitives like locks, semaphores, and monitors to…